MIPS Datapath

The datapath consists of all units that hold or operate on data

within a processor. In MIPS the datapath includes the register file,

the ALU, and memory. While there is only one memory, MIPS has separate

caches for data and instructions, and they are part of the datapath.

We are going to look at the three types of MIPS instructions

and see what the datapath looks like. The instructions are:

- memory reference (load and store)

- arithmetic/logic (leaving out the immediate instructions

for simplicity)

- branch

All instructions include the following steps:

- send the PC to memory and fetch the instruction

- read one or two registers, specified by Rs and Rt in

the instruction; some read one register, some read two

After these steps, each of the types above are handled differently.

- memory reference instructions use the ALU to calculate

the address, then perform a memory read or write

- arithmetic/logic instructions use the ALU to execute the

instruction, then write the result to a register

- branch instructions use the ALU to execute the comparison

to determine whether to take the branch, and if the

condition is true then the PC is updated

We are going to look at the hardware components used for each

of these, and then see how they fit together.

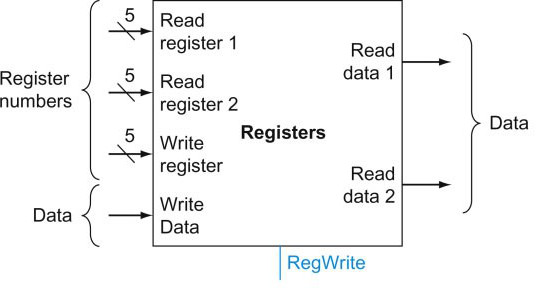

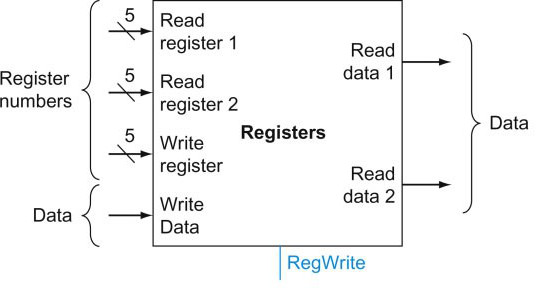

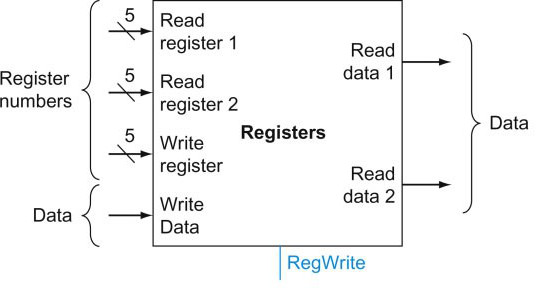

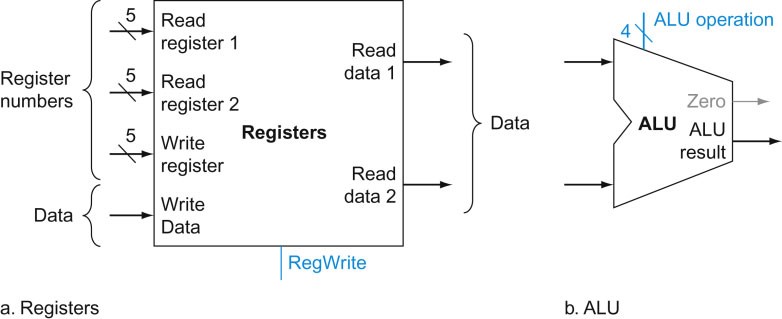

The Register File

- The register file is a unit that contains the 32 general

purpose registers. Any register can be read or written by

specifying the register number.

- The register file has two 5 bit inputs that specify the numbers of

the registers to be read. The register file can read and output

the two registers at the same time.

- The register file also has a 5 bit input that specifies the number

of the register to write. If the RegWrite control line is asserted

(set to 1), then the data on the WriteData lines is written to

the register specified by the write register lines.

- The register file can read and write during the same clock

cycle.

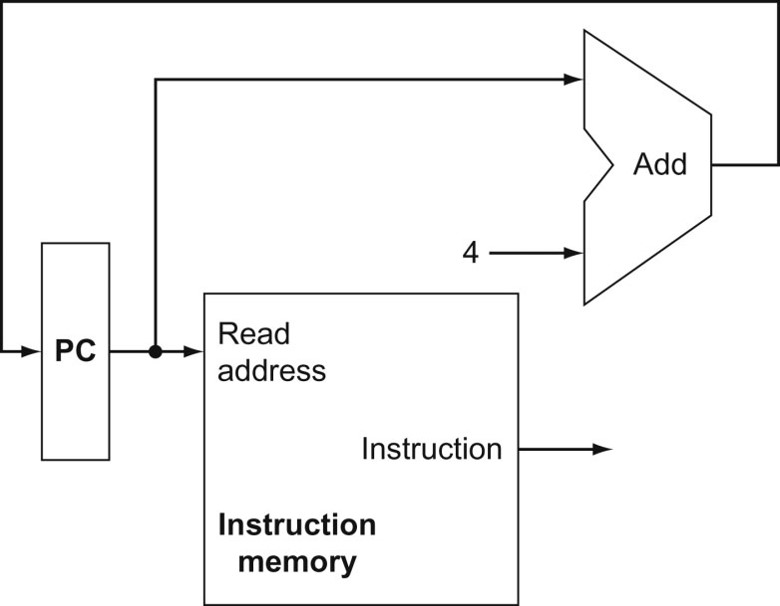

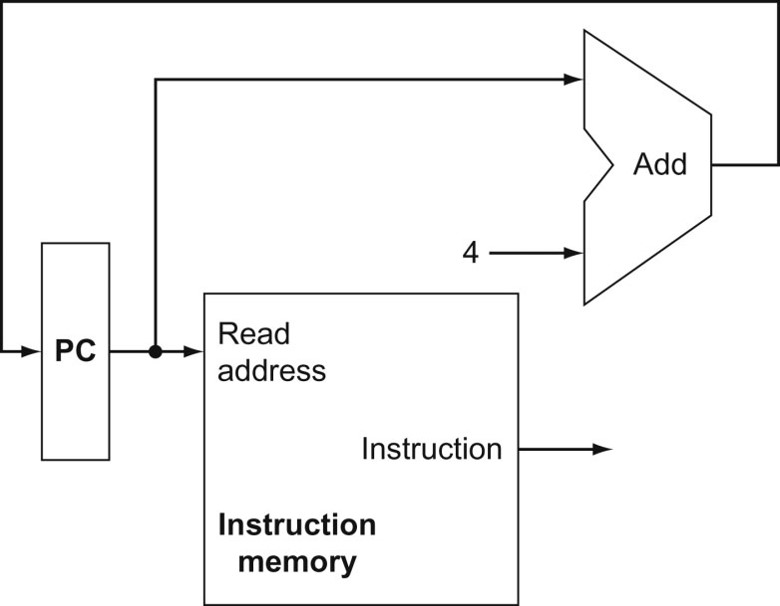

Instruction Fetch

- The address from the PC goes to the instruction memory, which

returns the instruction.

- The PC goes to an adder which adds 4 to get the next value of

the PC; there is a separate adder dedicated to updating the

PC.

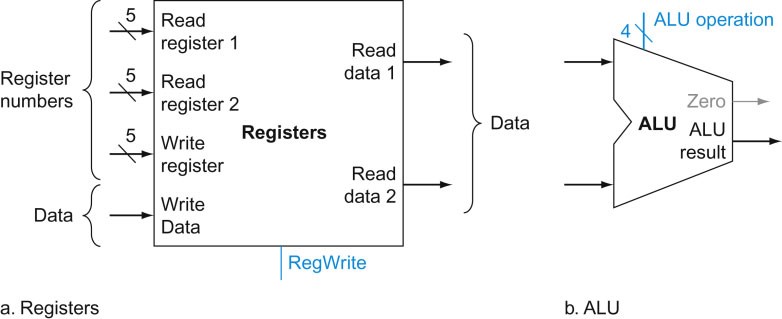

Executing R-type Instructions

The format of an R-type instruction is op Rd, Rs, Rt, such as

or $t2, $t4, $t5.

- The Read data outputs from the register file contain the values

read from the Rs and Rt registers. This is the input to the ALU.

The ALU Operation

input specifies what operation the ALU should perform.

- The ALU result will be sent to the Write Data input of

the register file. The Write register input of the register file

specifies which register (Rd) is written.

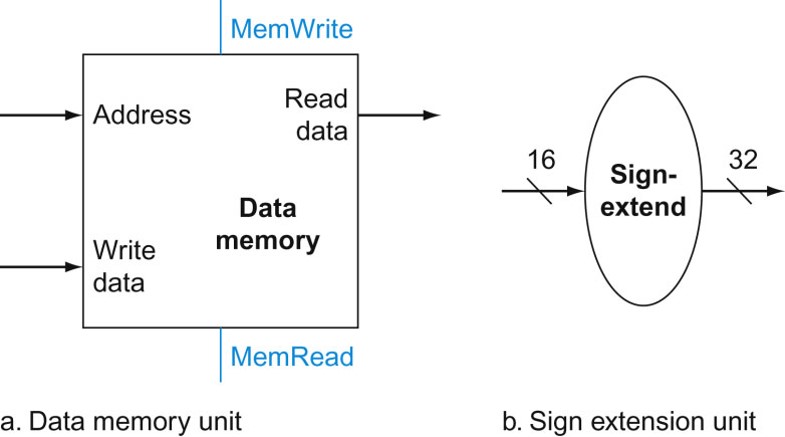

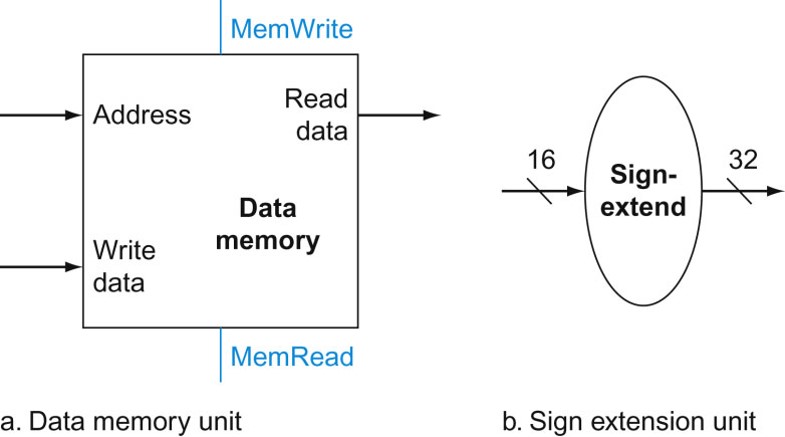

Executing Load and Store Instructions

The format of a load/store instruction is op Rt, offset(Rs), such as

lw $t2, 8($t5).

- Load and store instructions compute the memory address by

adding the offset (the 16 bit immediate operand) to the

second register (Rs).

- The immediate operand is signed, so it must be sign extended

to 32 bits before it can be added. The CPU has a unit for

this operation.

- After the memory address is computed it is sent to the

data memory.

- If the instruction is a store, the register to be stored (Rt)

must also be read from the register file and placed on the

data memory on the Write data input. The MemWrite input to the data memory

is asserted, and the data is written.

- If the instruction is a load, the MemRead input to the data

memory is asserted. The data at the address is place on the

Read data output of the data memory. This data is written

to the register file in Rt.

- From the above steps we can see that the ALU, data memory, and register

file are also needed to execute these instructions.

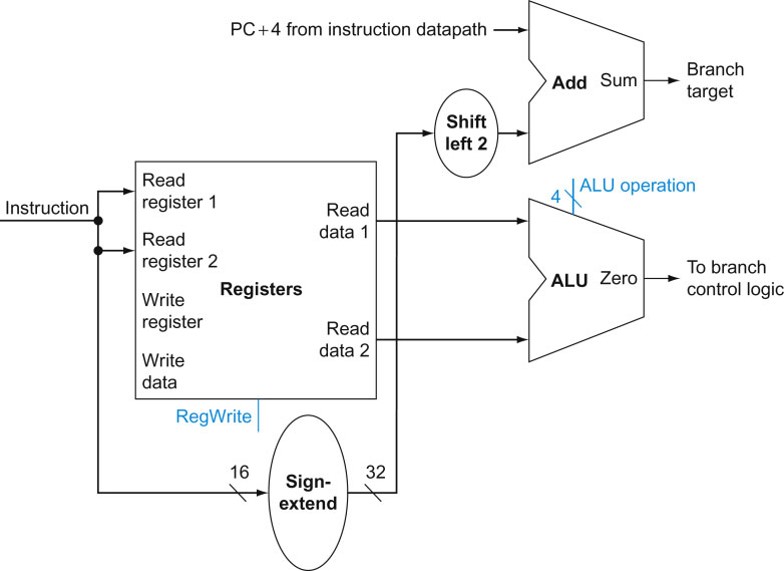

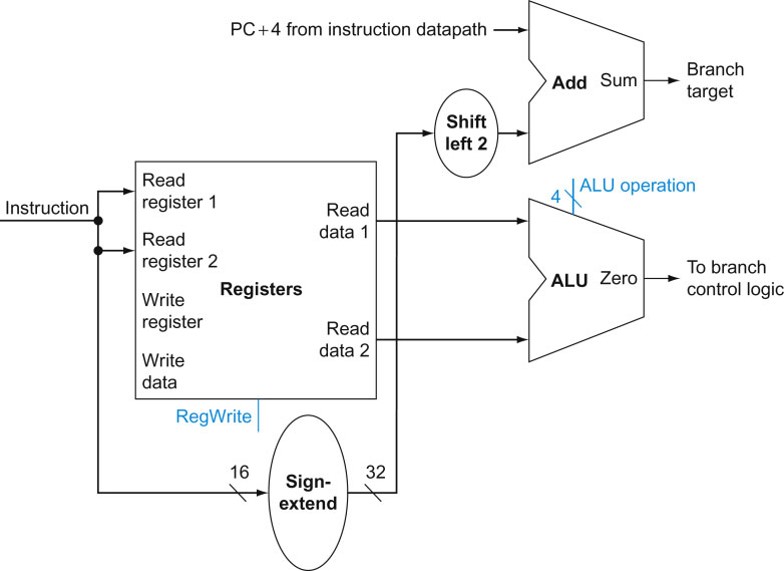

Executing Branch Instructions

The format of a branch instruction is op Rs, Rt, label, such as

beq $t2, $t4, loop. Recall that the label is translated into

an offset which specifies the number of statements between the branch

and the branch target.

- The offset is actually the number of statements between the

the branch target and the statement after the branch. This is

because the PC is always updated (PC <- PC + 4) during

instruction fetch

to contain the address of the next statement.

- The offset must be shifted left two bits to convert it from the

number of statements to the number of bytes. Then it can be

added to the PC if the branch condition is true.

- The branch condition must be evaluated to determine

whether to update the PC with the offset calculated in the

previous item. The values of

Rs and Rt are read from the register file and sent to the ALU

for comparison. The result of the comparison is sent to a

unit that will test the result and update the PC if required.

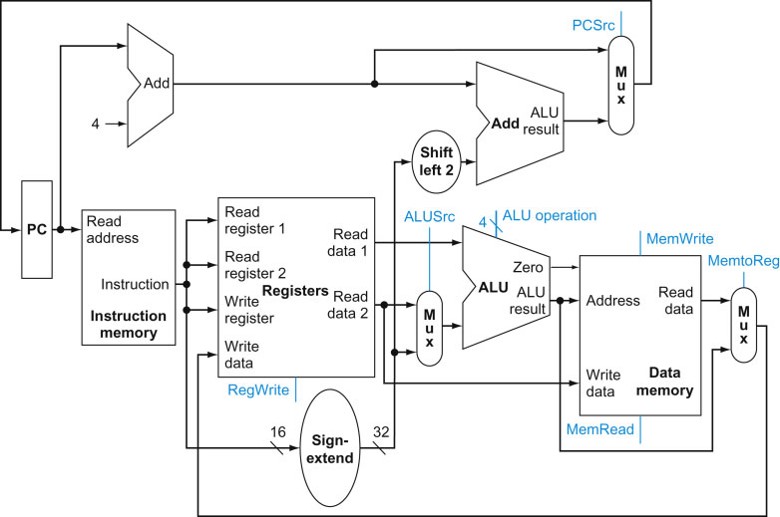

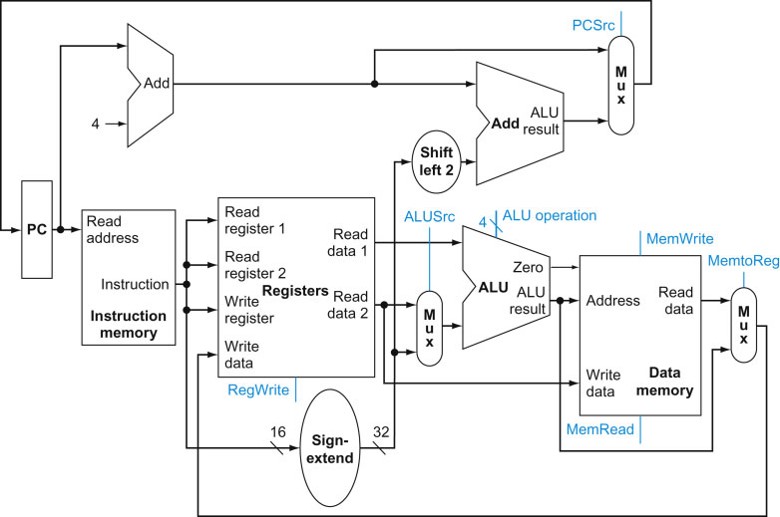

A Single Datapath

These separate paths are combined into one single datapath that

handles all instructions, and also includes the instruction fetch.

To combine them we need to add

some multiplexers. Recall that a multiplexer is a circuit

that has multiple data inputs and one output. It uses control inputs

to choose which data input will be the output. It can be thought of

as a selector, choosing one of a set of inputs. There are a few

places where we need multiplexers in our datapath:

- In an R-type instruction, the inputs to the ALU are the

outputs of the register file. But in a load/store, the

inputs to the ALU are one output of the register file and

the sign extended immediate operand (the offset). Thus

a multiplexer is needed for the second operand, to choose

whether it's a register or the offset.

- In an R-type instruction, the output of the ALU is written

to the register file. In a store instruction, the output

of the data memory is written to the register file. Another

multiplexer is needed here.

- In a non-branch instruction, the PC is updated by adding

4. In a branch, if the branch condition is true, the PC is

further updated to the address of the branch target. This

requires a third multiplexer.

The images in this handout are taken from "Computer Organization and

Design" by Patterson and Hennessy.

Email Me |

Office Hours |

My Home Page |

Department Home |

MCC Home Page