- What is 1K represented in hex?

- What is 1M represented in hex?

- How many lines are in the cache? Give your answer both as a base 10 number (you can represent the number using K or M) and as a power of two.

- How many blocks are in main memory? Give your answer both as a base 10 number (you can represent the number using K or M) and as a power of two.

- How many bits are in a memory address?

- How many bits of the memory address are needed to identify the position of a byte within a block (the offset)?

- How many bits of the memory address are needed to identify the block?

- How many bits of the memory address are needed for the tag?

- How many blocks of main memory are there?

- How many bits are needed for the tag, block, and offset fields?

- To which cache line will the memory address 0x63FA16 map?

- How many blocks of main memory are there?

- How many bits are needed for the tag, block, and offset fields?

- To which cache block will the memory address 0x13A4498A map?

- How many blocks of main memory are there?

- What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag and offset fields?

- To which cache block will the memory address 0xD87216 map?

- How many lines are in the cache?

- Show the main memory address format that allows us to map addresses from main memory to cache. Be sure to include the fields as well as their sizes.

- How many lines are in the cache?

- How many bits are in an address?

- Show the main memory address format that allows us to map addresses from main memory to cache. Be sure to include the fields as well as their sizes.

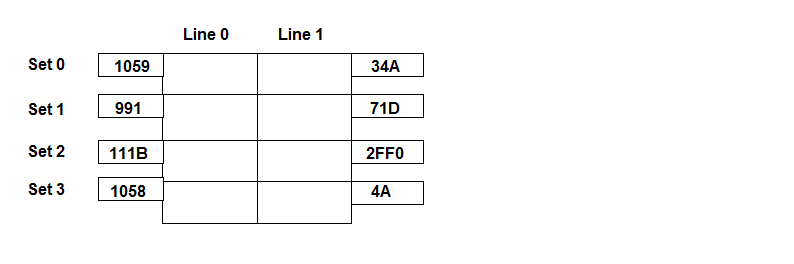

- Given the address 0x4AE7, which set does it map to? Is it in the cache? If so, in which line of the set?

- Given the address 0x10592B, which set does it map to? Is it in the cache? If so, in which line of the set?

- Given the address 0xCA86, which set does it map to? Is it in the cache? If so, in which line of the set?

Terms

Be familiar with the meaning of the following terms.

| cache hit | cache miss | |

| hit rate | miss time | |

| hit time | miss penalty | |

| direct mapped cache | fully associative cache | |

| set associative cache | levels of cache |

Email Me |

Office Hours |

My Home Page |

Department Home |

MCC Home Page

© Copyright Emmi Schatz 2021